研究目的

- ブートが高速で、コンパクトなカーネルを実装する。

- Codesegment と Datasegment をカーネルに実装するにあたって、メモリ管理の役割とどう合致するのかを検証する。

- 上記を確認したら CbC を用いて、動作が軽く落ちにくいカーネルを実装する。

- モデル検証に対応し、エラー予測を可能にする

- カーネルパニックをなくす

- Mach-O を ELILO でロードし、64bit で動作可能にする

ELILO

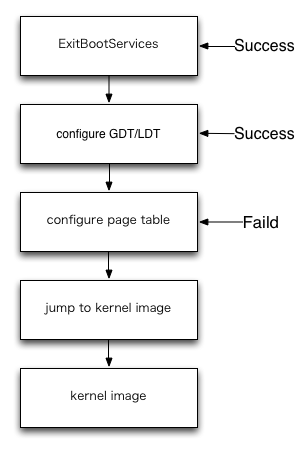

現状

ELILO

目標

- Page Table を初期化

- 一度 Paging を disable

- CR3 レジスタに初期化した Page Table を登録

- 再度 Paging を enable

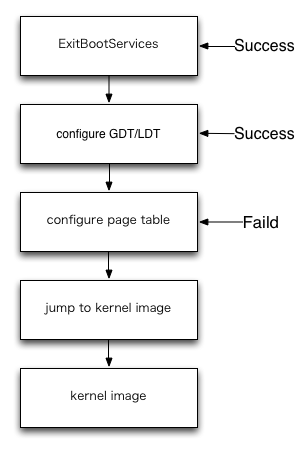

目標 [EFI version]

- memmap を設定

- 新しく仮想メモリ用に memmap を作る

- irq をセーブして、pgd を作る[TLB をフラッシュ]

- UEFI API SetVirtualAddressMap を call

- pgd を登録して、irq をリストア[TLB をフラッシュ]

どちらかの方法で、ELILO 内に Page table を作る

Page Table を登録する方法

Intel のマニュアルを参照

Page Table を登録する方法

Intel のマニュアルを参照

- segment descriptor CS の L ビット をクリアして、64 bit mode から compatibility mode へ

- CR0.PG をクリアして Paging を disable

- CR3 に、初期化したページテーブルのアドレスを入れる

- CR0.PG に 1 をセットして Paging を enable する

- 64 bit mode に戻す

Page Table を登録する方法

UEFI のマニュアルを参照

- ……っていうのを、SetVirtualAddressMap() がやってくれるんじゃないか

- つまり、EFI用の Memory map を設定すれば、仮想メモリが作れるんじゃ?

今週すること